多输出函数的化简@

计数型节拍分配器

由二进制计数器和译码器组成

译码器输出高电位或脉冲信号

1:完全给定与不完全给定

用卡诺图法化简逻辑函数的基本步骤:

1.将逻辑函数表示在卡诺图上

2.genuine实质最小项确定所有的必要极大圈

3.如果所选出的所有必要及大图已覆盖卡诺图上全部1小方格,那么这些必要及大圈的集合就是卡诺图上的最小覆盖

4.如果还有标1的小方格未被上述的必要极大圈覆盖,那么再加上选择最少的极大圈覆盖剩余的标1小方格,即获得最小覆盖

5.写出最小覆盖所对应的逻辑表达式,即最简与或式

函数是激励函数

哪些是自变量,哪些是函数,函数是激励函数。计数器的输出一般是触发器的输出。

1:异步计数器:LD和CLR信号加载在CLK端。

2:同步计数器;LD和CLR信号加载在数据端

3:74LS163周期×2频率减半

4:并入-chuan'chu

计数器:1强制位计数器2预置位计数器3修正式计数器

进位传递函数

1:把脉冲分成信号线。

时序电路的分析是根据逻辑电路图得到反映时序电路工作特性的状态表及状态图

D锁存器要求:

在控制(时钟)输入CLK有效期间内,输入数据D稳定不变

边沿触发器:在控制信号的有效边沿(前沿或后沿)时接收数据

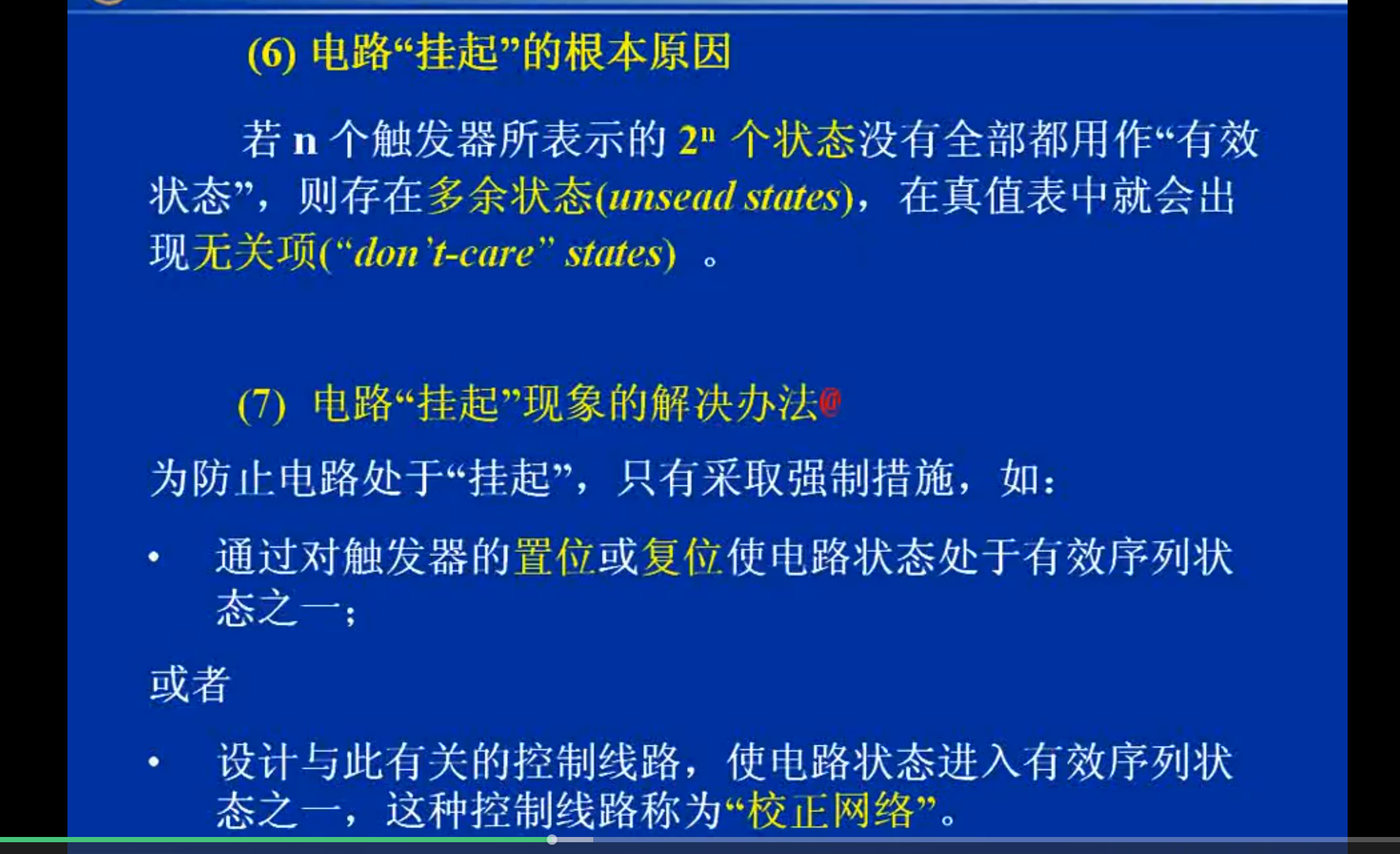

电路特性描述:该电路有16个特性,只要电路的初始状态为状态图闭合环中的某一状态,在时钟脉冲作用下,电路将按箭头所指方向在闭合环中8个状态间循环,这是一个模8步进码计数器,时钟脉冲就是计数信号。在闭环以外的8个状态称为“无效序列”,这种电路称为格雷码计数器或Johnson计数器,也叫“自恢复纽环移位寄存器

电路挂起的解决方法:

1.无序列的次态无关项全部指向0;

2.打断一处”无效序列链“,令其指向有效序列

3.根据真值表和卡诺图研究无效序列的生成规律尽可能只改变某一触发器的输入网络,同时进行最简设计

1:"无为“

双稳态元件是构成存储电路的基本模块,通常指锁存器或触发器,特点是

1.有俩个稳定状态,分别表示存储数码0或1

2.在一定的出发信号作用下,它可从一个稳态翻转到另一个稳态

作用:每个稳态原件保存一位二进制数,对应一个状态变量

三态是指器件的输出有三种状态:即逻辑0,逻辑1和高阻抗状态,最基本的三态器件时三态缓冲器,又称为 三态门或者三态驱动器

三态门或者三态驱动器

当译码器的输出编码位数少于输入编码位数时,这种器件称为编码器

若需要输入端n > 8的编码器,则可用多片74LS148连起来

最常用的译码器是二进制译码器,又称为n-2n译码器

为了提高电路的速度,提高器件的利用率,从而减少IC的数量,也减少外部的连接线和提高电路的可靠性,需要对电路对从逻辑表达式直接画出的逻辑电路图进行转换,尽可能使其用同一类型的输出端带非的门来实现

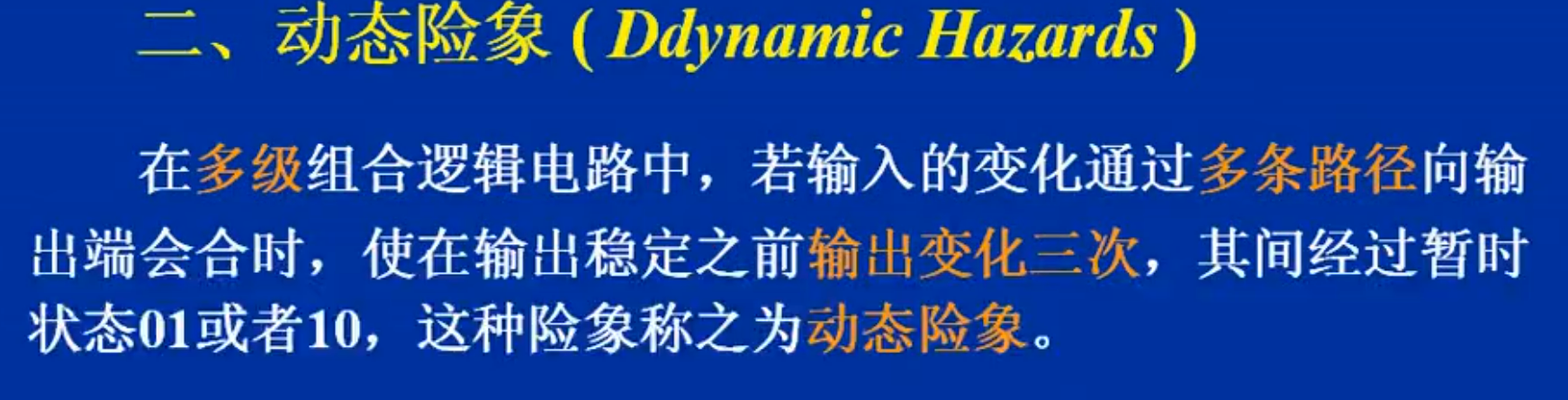

竞争现象:同一信号或同时变化的某些信号,经过不同路径到达某一点时有时差,这种现象称为竞争

由于临界竞争的存在,在输出端得到稳定输出之前,输出中有一短暂的错误输出,这种现象称之为险象,通常将险象分为静态险象和动态险象

静态险象分为功能险象和逻辑险象

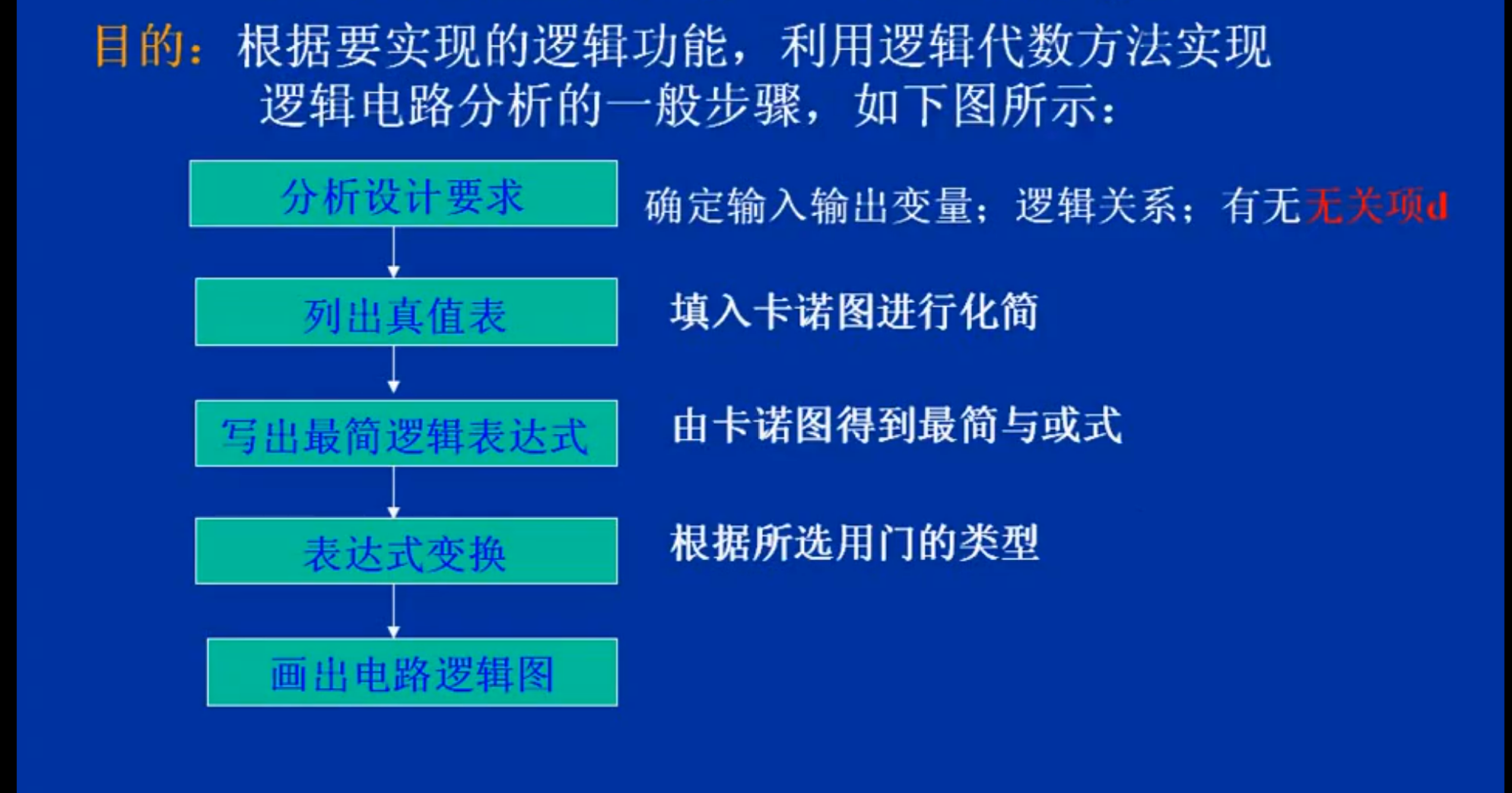

组合电路设计

目的:根据要是心啊的逻辑功能,利用逻辑代数方法实现逻辑电路分析的一般步骤

电路分析的目的:根据给定电路,分析该电路输出与输入之间的逻辑关系,得出电路的逻辑功能的描述,进而评估此电路的性能,还可进一步改进电路